Research

CAREER: Power Aware Scheduling for Real-Time Embedded Systems

Funding Source: National Science

Foundation (NSF), $400,000 + 16,000 (REU supplement), 2006 - 2011

Investigator: Dr. Gang Quan (single PI)

Over the past few decades, we have seen tremendous improvement of real-time embedded systems, ranging of functionality, applications, and performance. From cell phones, digital TV, microwave ovens, automobiles, to implantable artificial hearts, everyone interacts with such systems on a daily basis. Driven by today’s IC and wireless technology, we are entering a period of great advancement in the capabilities and pervasiveness of battery-operated real-time embedded systems into our professional and personal lives. Many real-time applications, especially those for portable mobile applications demand longer battery life for the sake of mobility. Current battery technology, with its 5-10% annual capacity improvement cannot effectively address this problem. In fact, the International Roadmap for Semiconductors (ITRS) estimates that a 20-times dynamic power consumption gap and as much as 800-times standby power consumption gap for portable devices need to be closed by the year of 2016. On the other hand, even in a power-rich platform, the rapidly elevated power/energy consumption has also raised serious concerns with regards to the reliability of the system, as well as the cost to deal with the heat dissipation. Our current research focuses on developing appropriate real-time scheduling algorithms that incorporates advanced power manageable features (such as dynamic voltage scaling, dynamic power down) in state-of-art computer architecture to meet the increasingly stringent timing requirements, as well as optimize other performance metrics, such as power/energy consumptions and temperatures, for real-time applications.

Our research consists of a two-pronged approach, consisting of both a theoretical research and a practical validation. We believe that a successful research program must build upon a solid theoretical research. On the other hand, due to its application nature, the theoretical research for real-time embedded systems needs to be validated not only based on idealized, simplified theoretical models but also under more practical scenarios.

· Theoretical Research

Our theoretical research follows the simple principle in scientific research, i.e. from the simple model to the complex model. We started our power-aware real-time scheduling research from the simplest problem, i.e. the uniprocessor system with hard real-time requirements. One of our papers was awarded the "Best Paper Award" from the 38th Design Automation Conference (DAC), and another one was selected as one of the top three "Most Influential Papers" in 2002 Design Automation & Test in Europe (DATE). We then extended our research in a number of ways, this includes: extending real-time system models with more complicated Quality-of-Service (QoS) requirements rather than the simple hard real-time constraints; incorporating more practical processor models; extending the energy model to include both dynamic and leakage components; studying the system-wide overall energy reduction instead of energy-savings for the processor alone.

Figure 1 Power Aware Real-Time Scheduling Research Roadmap

Currently, we are very interested in the power-aware real-time scheduling for multi-core type of architecture. The multicore architecture is becoming the mainstream platform for the following reasons. First, the transistor size continues to shrink, compounding the enormously high clock frequency, will lead to the exponentially escalating heat dissipation that is beyond any reasonable and cost-effective thermal control. Second, the growing memory-processor gap results in the diminishing return of processor performance improvement. Third, the exploitation of instruction level parallelism, which has been a key factor in driving the processor performance, cannot be sustained forever by processor innovations. As a result, the industry is switching its paradigm from high performance uniprocessor computing to highly parallel computing.

· Practical Validation

Theoretical research is often based on theoretically idealized models, whereas practical applications must deal with other important details added to the model. Studying power aware scheduling techniques with real-time applications can be extremely valuable. It helps to evaluate and validate the scheduling solutions and modeling assumptions, and further to identify new research problems. To this end, we have constructed two hardware test platforms that allow us to analyze and assess key properties of our theoretical work under different yet more accurate environmental conditions.

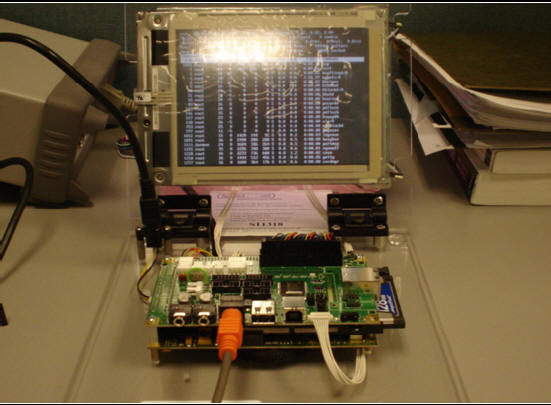

The first test bed, primarily for uniprocessor scheduling verification, is based on the BitsyXb development board (with Intel Xscale PXA270), developed by Applied Data Systems, and Linux 2.6 kernel. We modified the kernel to accommodate pertinent real-time information that separates between real-time processes and other non-real-time processes. Multiple scheduling policies can be co-existed in the kernel and hot-swapped during run-time for the fair comparison of different scheduling schemes. Modifications are also made to the scheduler to enable the voltage/frequency scaling. We also implemented a number of utilities including period/aperiod process generation, deadline verification, profiling, and power measurement.

Figure 2 Testbed Based on BitsyXb Commercial Embedded Development Board.

The second test bed is developed on the reconfigurable hardware, i.e.Xilinx’s development board ML402, and primarily targets at the multicore-type architecture. The hardware architecture (as shown in the following figure) consists a number of processing elements (PEs) connected with interconnection network. Each PE consists a processor core, i.e. MicroBlaze or PowerPC, or other special functional unit, a small scratch-pad memory, a customized clock control IP, and a customized timer (for MB only since PPC has built-in timer already). With the customized clock IP, each PE can dynamically change its working frequency during run-time by software.

Figure 3 The Reconfigurable Multicore Architecture.