## Contents

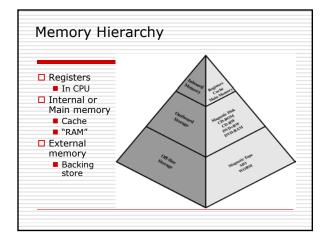

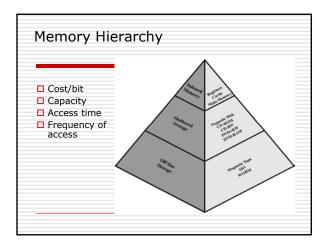

Memory System Overview

$\square$

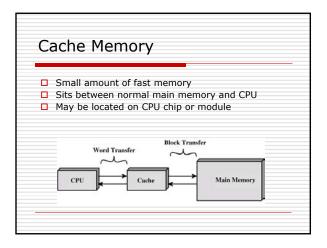

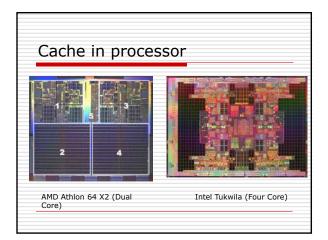

- Cache Memory

- □ Internal Memory

- External Memory

- Virtual Memory

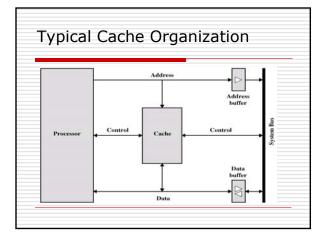

|    | ache operation                                                                         |

|----|----------------------------------------------------------------------------------------|

|    | CPU requests contents of memory<br>location                                            |

| 1  | Check cache for this data                                                              |

| [  | If present, get from cache (fast)                                                      |

| [  | If not present, read required block from<br>main memory to cache                       |

| [  | Then deliver from cache to CPU                                                         |

| A١ | g memory access time = Hit time_L1 + Miss rate_L1 x Miss penalty_L1                    |

| Mi | ss Penalty <sub>L1</sub> = Hit time $_{L2}$ + Miss rate $_{L2 x}$ Miss penalty $_{L2}$ |

| Two levels of memory                                   |

|--------------------------------------------------------|

| Level 1 access time 0.01 us, Level 2 access time 0.1us |

| 95% memory accesses are found in level 1               |

| Average memory access time for each word?              |

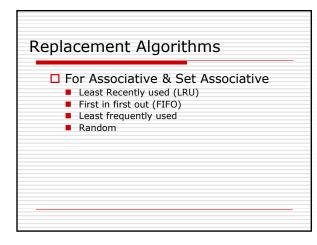

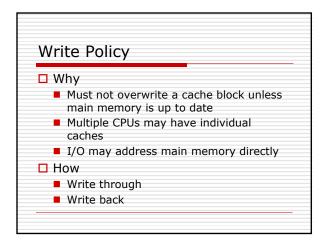

| Cache Design                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Size</li> <li>Mapping Function</li> <li>Replacement Algorithm</li> <li>Write Policy</li> <li>Block Size</li> <li>Number of Caches</li> </ul> |

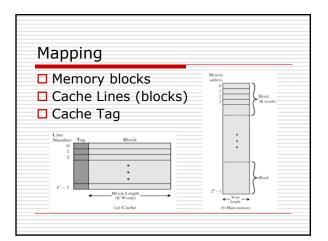

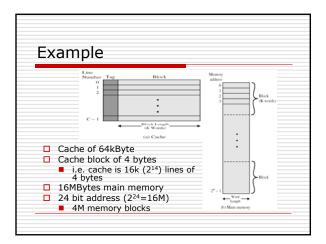

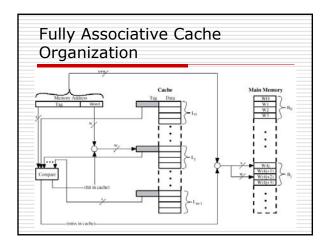

| <br>ddress structure                                                                                       |

|------------------------------------------------------------------------------------------------------------|

| Address is in two parts ( <b>s+w</b> )                                                                     |

| Most Significant <b>s</b> bits specify one memory block                                                    |

| <ul> <li>Block address: which block should be read or written</li> </ul>                                   |

| <ul> <li>The s bits are split into a cache line field r and a<br/>tag of s-r (most significant)</li> </ul> |

| Least Significant w bits identify unique byte                                                              |

| <ul> <li>Block shift: within the block, which byte should be read<br/>or written</li> </ul>                |

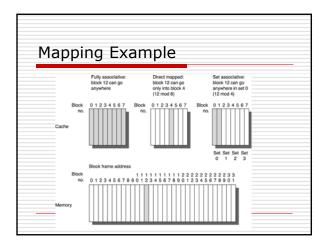

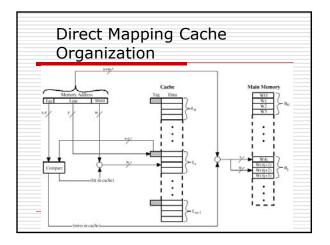

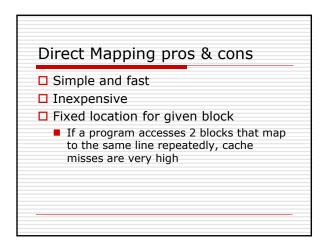

| Dir | ect Mapping                                                   |

|-----|---------------------------------------------------------------|

|     | ach block of main memory maps to only ne cache line           |

| -   | i.e. if a block is in cache, it must be in one specific place |

| D۲  | łow                                                           |

|     | I i=j modulo m                                                |

|     | i: cache line number                                          |

|     | j: memory block number                                        |

|     | m: number of total lines in the cache                         |

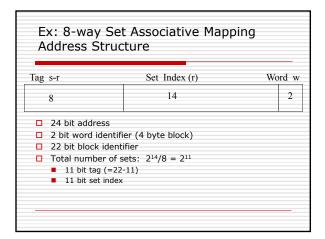

| Tag s-r                                           | s-r Line of block index r                                                                                      |           |  |  |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------|--|--|

| 8                                                 | 14                                                                                                             | 2         |  |  |

| <ul><li>Total cache</li><li>22 bit bloc</li></ul> | identifier (4 byte block)<br>e lines: 2 <sup>14</sup> (or the number of blocks i<br>k identifier<br>g (=22-14) | n caches) |  |  |

| Tag 22 bit                                                                                | Word<br>2 bit |

|-------------------------------------------------------------------------------------------|---------------|

| 22 bit tag stored with each 4 bytes of data                                               |               |

| Compare tag field with tag entry in cache to ch<br>for hit                                | eck           |

| Least significant 2 bits of address identify which byte is required from the 4 byte block | ı             |

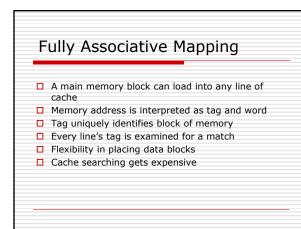

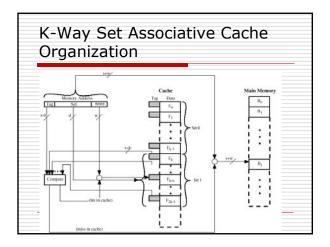

| Cache lines is divided into a number of groups, i.e., sets                     |

|--------------------------------------------------------------------------------|

| A given block maps to only one set, but can be<br>any line in the set          |

| How                                                                            |

| <ul> <li>i=j modulo v</li> <li>v: number of total sets in the cache</li> </ul> |

| Trade off between direct mapping and fully<br>associative mapping              |

| Line Size                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Larger blocks reduce the number of blocks that fit into a cache.</li> <li>Larger blocks make each additional word is less likely to be needed in the near future.</li> </ul> |

| Contents                                                                             |               |

|--------------------------------------------------------------------------------------|---------------|

| Memory System Overview Cache Memory                                                  |               |

| <ul> <li>Internal Memory</li> <li>External Memory</li> <li>Virtual Memory</li> </ul> |               |

|                                                                                      | $\Rightarrow$ |

| Internal memory types |  |

|-----------------------|--|

| DRAM vs. SRAM         |  |

| Semiconductor Memory Types             |                    |                           |                 |             |  |

|----------------------------------------|--------------------|---------------------------|-----------------|-------------|--|

| Метогу Туре                            | Category           | Erasure                   | Write Mechanism | Volatility  |  |

| Random-access<br>memory (RAM)          | Read-write memory  | Electrically, byte-level  | Electrically    | Volatile    |  |

| Read-only<br>memory (ROM)              |                    | M)                        | Masks           |             |  |

| Programmable<br>R OM (PR OM)           | Read-only memory   | Not possible              |                 |             |  |

| Erasable PROM<br>(EPROM)               |                    | UV light, chip-level      | Electrically    | Nonvolatile |  |

| Electrically Erasable<br>PROM (EEPROM) | Read-mostly memory | Electrically, byte-level  | 1               |             |  |

| Flash memory                           |                    | Electrically, block-level | -               |             |  |

| - |  |

|---|--|

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

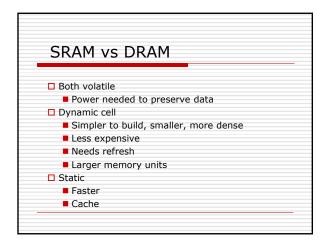

## Dynamic RAM

| Bits stored as charge in capacitors           |

|-----------------------------------------------|

| □ Charges leak -> Need refreshing (and        |

| therefore refresh circuits) even when powered |

| Simpler construction                          |

| Smaller per bit                               |

| Less expensive                                |

| Slower                                        |

| Main memory                                   |

| Static R | AM                                                     |

|----------|--------------------------------------------------------|

| Bits sto | red as on/off switches                                 |

|          | ges to leak and therefore no<br>ng needed when powered |

| More cor | nplex construction                                     |

| Larger p | er bit                                                 |

| More exp | pensive                                                |

| Faster   |                                                        |

| Cache    |                                                        |

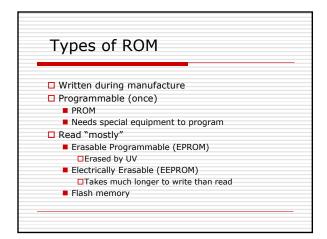

| Permanent storage       |  |

|-------------------------|--|

| Nonvolatile             |  |

| Usage                   |  |

| Library subroutines     |  |

| Systems programs (BIOS) |  |

| Function tables         |  |

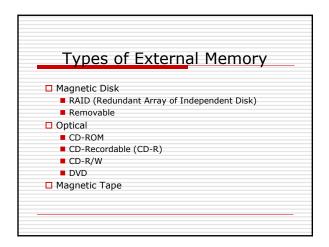

| Types of external memory |  |

|--------------------------|--|

|                          |  |

|                          |  |

|                          |  |

|                          |  |

|                          |  |

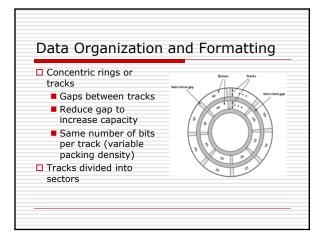

| P | lagnetic Disk                                                                     |

|---|-----------------------------------------------------------------------------------|

|   | Read and Write Mechanisms                                                         |

|   | <ul> <li>Recording and retrieval via conductive coil called a<br/>head</li> </ul> |

|   | May be single read/write head or separate ones                                    |

|   | During read/write, head is stationary, platter rotates                            |

|   | Write                                                                             |

|   | Current through coil produces magnetic field                                      |

|   | Pulses sent to head                                                               |

|   | Magnetic pattern recorded on surface below                                        |

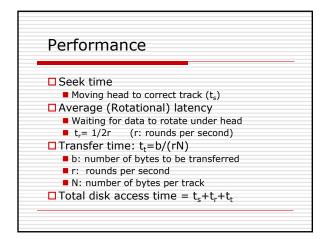

| Example                                                                                               |               |

|-------------------------------------------------------------------------------------------------------|---------------|

| Seek time = 4ms                                                                                       |               |

| Rotation speed = 7500rpm                                                                              |               |

| 512 bytes/sector, 500 sectors/t                                                                       | rack          |

| A file with total 2500 sectors                                                                        |               |

| Assume:                                                                                               |               |

| <ul> <li>Sequentially stored</li> </ul>                                                               |               |

| <ul> <li>Randomly stored</li> </ul>                                                                   |               |

| 1. Ts= 4ms, Max Tr = 60/7500=8ms                                                                      |               |

| 2500 sectors → 5 tracks Tt for each track = b/rN                                                      |               |

| Total disk access time = (4 + 8 + 8) + 8 * 4 = 52<br>(assume no seek and rotation time except for the |               |

| 2. Ts = 4ms, Avg Tr= 4ms,                                                                             | III'SL U'ALK) |

| Tt for each sector =                                                                                  |               |

| (1x 512) * 60 /(7500 * (500 x 512)) = 8/500 r<br>Total disk access time = 2500 x (4 + 4 + 8/500) =    |               |

|      | lit memory into equal sized, small chunks -<br>ge frames |

|------|----------------------------------------------------------|

|      | ocate the required number page frames to a<br>ocess      |

| □ Ор | erating System maintains list of free frames             |

|      | process does not require contiguous page<br>mes          |

| 🗆 Us | e page table to keep track                               |

| Vi  | rtual Memory                                        |

|-----|-----------------------------------------------------|

|     | emand paging                                        |

|     | Do not require all pages of a process in            |

|     | memory                                              |

|     | Bring in pages as required                          |

| 🗆 P | age fault                                           |

|     | Required page is not in memory                      |

|     | Operating System must swap in required page         |

|     | May need to swap out a page to make space           |

|     | Select page to throw out based on recent<br>history |

| Ve do not need all of a process in memory for it<br>o run                   |

|-----------------------------------------------------------------------------|

| Ve can swap in pages as required                                            |

| o - we can now run processes that are bigger<br>han total memory available! |

| 1ain memory is called real memory                                           |

| lser/programmer sees much bigger memory -<br>irtual memory                  |

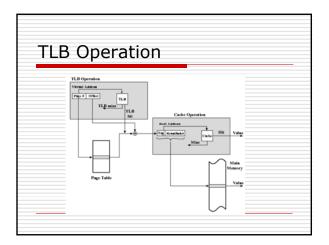

| Translation Lookaside Buffer<br>(TLB)                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Two physical memory<br/>accesses/virtual memory<br/>reference</li> <li>Page table</li> <li>Desired data</li> </ul> |

| <ul> <li>TLB</li> <li>A special cache for page table entries</li> </ul>                                                     |

|                                                                                                                             |