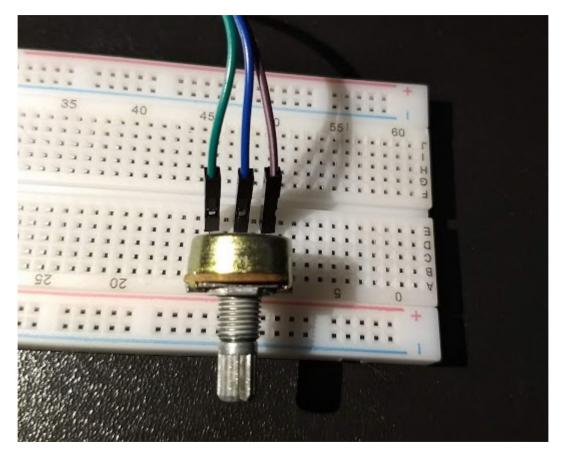

Mount potentiometer from Starter Kit onto Breadboard and insert a wire for each pin

Wires on the ends go to GND and 3V3 on the board, center wiper goes to P1.1

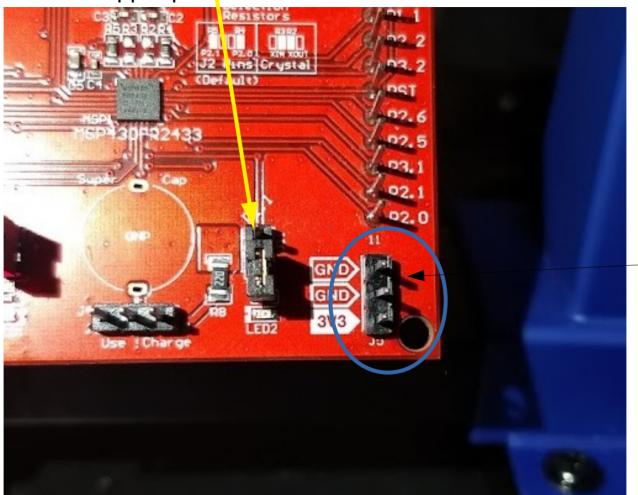

P1.1 Analog A1 Input (also Green LED) – remove jumper expose Upper pin

Ground And +3V

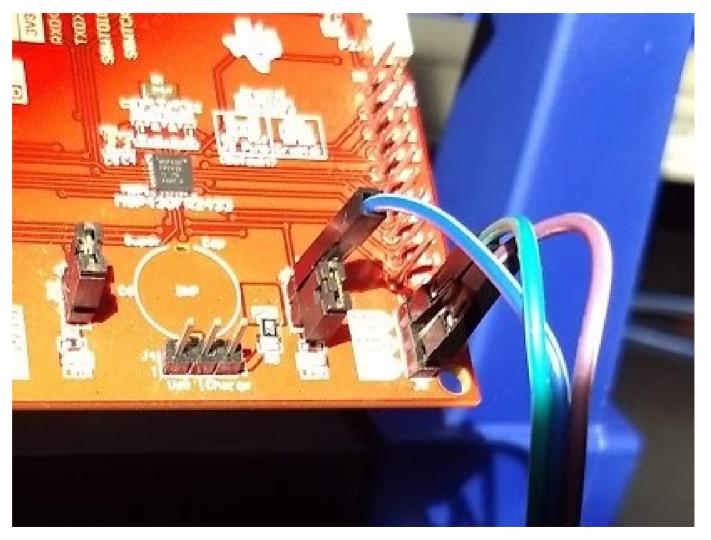

Connections for Potentiometer – Center connect to P1.1, ends to GND and 3V3

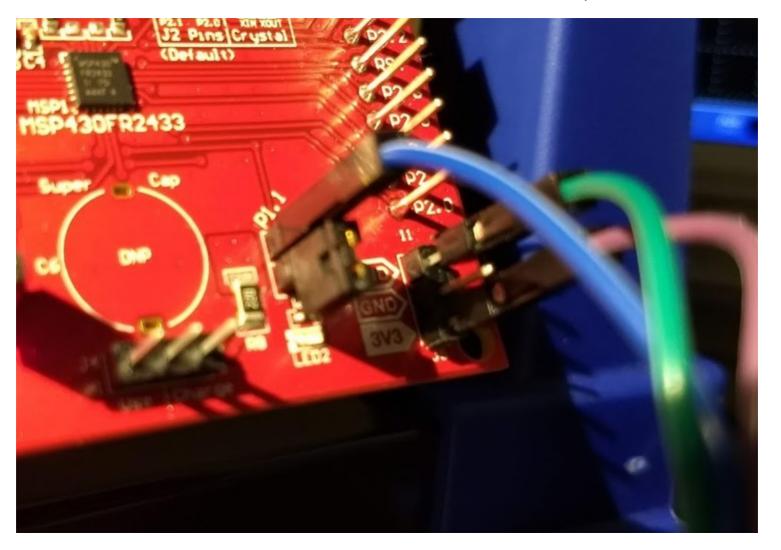

Another view of potentiometer connections to board

```

2

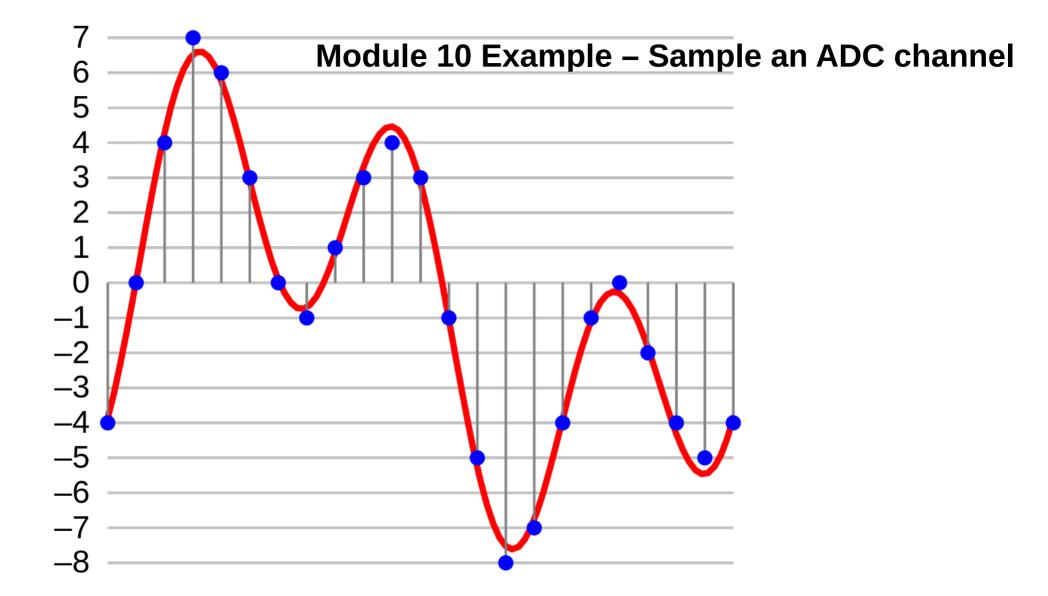

MSP430FR24xx Demo - ADC, Sample Al, AVcc Ref, Set LED if Al > 0.5*AVcc

//

Description: This example works on Single-Channel Single-Conversion Mode.

A single sample is made on Al with default reference to AVcc.

Software sets ADCSC to start sample and conversion - ADCSC automatically

cleared at EOC. ADC internal oscillator times sample (16x) and conversion.

In Mainloop MSP430 waits in LPM0 to save power until ADC conversion complete,

10

ADC ISR will force exit from LPMO in Mainloop on reti.

If Al > 0.5*AVcc, Pl.0 set, else reset.

12

Pl.1 is Al, jumper for Green LED will force 381 result

ACLK = default REFO ~32768Hz, MCLK = SMCLK = default DCODIV ~1MHz.

13

//

14

1//

15

//

MSP430FR2433

16

//

17

//

III

18

//

19

-- IRST

//

20

//

21

//

>--- P1.1/A1

P1.0 --> LED

22

//

23

//

24

Wei Zhao

Texas Instruments Inc.

26

sketch ADC UART 243301.ino

modified by HW -

27

28

place potentiometer

GND

29

- remove Green LED jumper

30

V+3

31

32

33

```

34

## 'Set Up part of the program'

```

#include <msp430.h>

35

36

37

unsigned int ADC_Result;

38

int main(void)

□{

41

WDTCTL = WDTPW | WDTHOLD;

// Stop WDT

// Configure GPIO

P1DIR |= BIT0;

// Set Pl.0/LED to output direction

45

// P1.0 LED off

P10UT &= ~BIT0;

// Configure ADC Al pin

48

SYSCFG2 |= ADCPCTL1;

// Disable the GPIO power-on default high-impedance mode to activate

5Θ

// previously configured port settings

4

52

PM5CTL0 &= ~LOCKLPM5;

53

```

```

54

// Clock System Setup ACLK = 32786, MCLK = SMCLK = 1MHz

55

bis SR register(SCG0);

// disable FLL

CSCTL3 |= SELREF REFOCLK;

// Set REFOCLK as FLL reference source

56

// clear DCO and MOD registers

57

CSCTL0 = 0;

58

CSCTL1 &= ~(DCORSEL 7);

// Clear DCO frequency select bits first

59

CSCTL1 |= DCORSEL 3;

// Set DCOCLK = 8MHz

5

60

CSCTL2 = FLLD 1 + 121:

// FLLD = 1, DCODIV = 4MHz

61

delay cycles(3);

bic SR register(SCG0);

// enable FLL

62

while(CSCTL7 & (FLLUNLOCK0 | FLLUNLOCK1));

// Poll until FLL is locked

63

64

CSCTL4 = SELMS DCOCLKDIV | SELA XT1CLK;

// set ACLK = XT1 = 32768Hz.

65

//DCOCLK as MCLK and SMCLK source

66

CSCTL5 |= DIVM1;

// Configure ADC10

68

69

ADCCTL0 |= ADCSHT 2 | ADCON;

// ADCON, S&H=16 ADC clks

ADCCTL1 |= ADCSHP:

// ADCCLK = MODOSC; sampling timer

70

71

ADCCTL2 |= ADCRES;

// 10-bit conversion results

// Al ADC input select; Vref=AVCC

72

ADCMCTL0 |= ADCINCH 1;

```

ADCIE |= ADCIE0;

73 74 // Enable ADC conv complete interrupt

## 'Loop' part of the program – Get a sample and wait for arrival

```

75

while(1)

76

77

➤ ADCCTL0 |= ADCENC | ADCSC;

// Sampling and conversion start

78

__bis_SR_register(LPM0_bits | GIE);

// LPM0, ADC ISR will force exit

79

// this line below waits until Return-From-Interrupt

80

if (ADC Result < 0x1FF)◀

81

// Clear Pl.0 LED off

82

P10UT &= ~BIT0;

83

else

P10UT |= BIT0;

84

// Set Pl.0 LED on

delay cycles(500000);

// Delay 0.5 second

85

86

87

```

```

// ADC interrupt service routine

89

90

#pragma vector=ADC VECTOR

interrupt void ADC ISR(void)

91

92

₽{

93

switch(ADCIV)

94

95

case ADCIV NONE:

break:

96

97

case ADCIV ADCOVIFG: // memory overflow - ADCMEM0 overflow

break:

98

case ADCIV ADCTOVIFG: // ADC conversion-time-overflow

99

break:

100

8

case ADCIV ADCHIIFG: // Comparator above upper threshold

101

102

break:

// Comparator below lower threshold

103

case ADCIV ADCLOIFG:

break:

104

case ADCIV ADCINIFG: // Comparator inside window

105

break:

106

107

case ADCIV ADCIFG:

// Conversion complete

ADC Result = ADCMEM0;

108

_bic_SR_register_on_exit(LPM0_bits);

// Clear CPUOFF bit from LPM0

109

break;

110

default:

111

112

break;

113

114

115

```